È ormai da molto tempo che non è più possibile aumentare le prestazioni dei sistemi di calcolo aumentando la loro frequenza di lavoro, ed è anche da molto tempo che la soluzione del problema è stata individuata nell'utilizzo del parallelismo di elaborazione. Ci troviamo quindi di fronte a sistemi di processamento multi o many-core eterogenei e asimmetrici: essi sono ormai tra noi, e il problema è renderli effettivamente utilizzabili all'industria, specie nell'ambito dei sistemi embedded e ciberfisici. È quello che ha cercato di fare open-next affrontando una molteplicità di scenari collegati dalla necessità di utilizzare architetture eterogenee e mutiprocessing asimmetrico, e che ha cercato di fare in collaborazione non solo con le aziende partner originarie del progetto ma anche con altre aziende che si sono affiancate via via nel tempo.

OPEN-NEXT - Strutture software real-time e open-source per piattaforme embedded industriali

OPEN-NEXT - Strutture software real-time e open-source per piattaforme embedded industriali

PROGRAMMING MODEL Identificazione e utilizzo dei modelli di programmazione di riferimento per l’esecuzione di applicazioni real-time parallele sulle piattaforme eterogenee multi/many-core identificate come casi d’uso del progetto. SISTEMI OPERATIVI REAL-TIME Creazione di stack complessi di OS per la gestione di architetture eterogenee multi/many-core. STRUMENTI DI ANALISI E DI SVILUPPO Creazione di un insieme di tool che facilitino l’utilizzo delle piattaforme computazionali sviluppate nelle attività precedentemente descritte e della loro integrazione in un unico IDE.

- Modelli di programmazione per architetture eterogenee multi/many-core con vincoli real-time - Stack complessi di sistemi operativi per il supporto di applicazioni real-time su architetture eterogenee multi/many-core - Strumenti per il build e la configurazione di stack complessi di sistemi operativi e per l'analisi di schedulabilita' dei moduli SW di una applicazione real-time

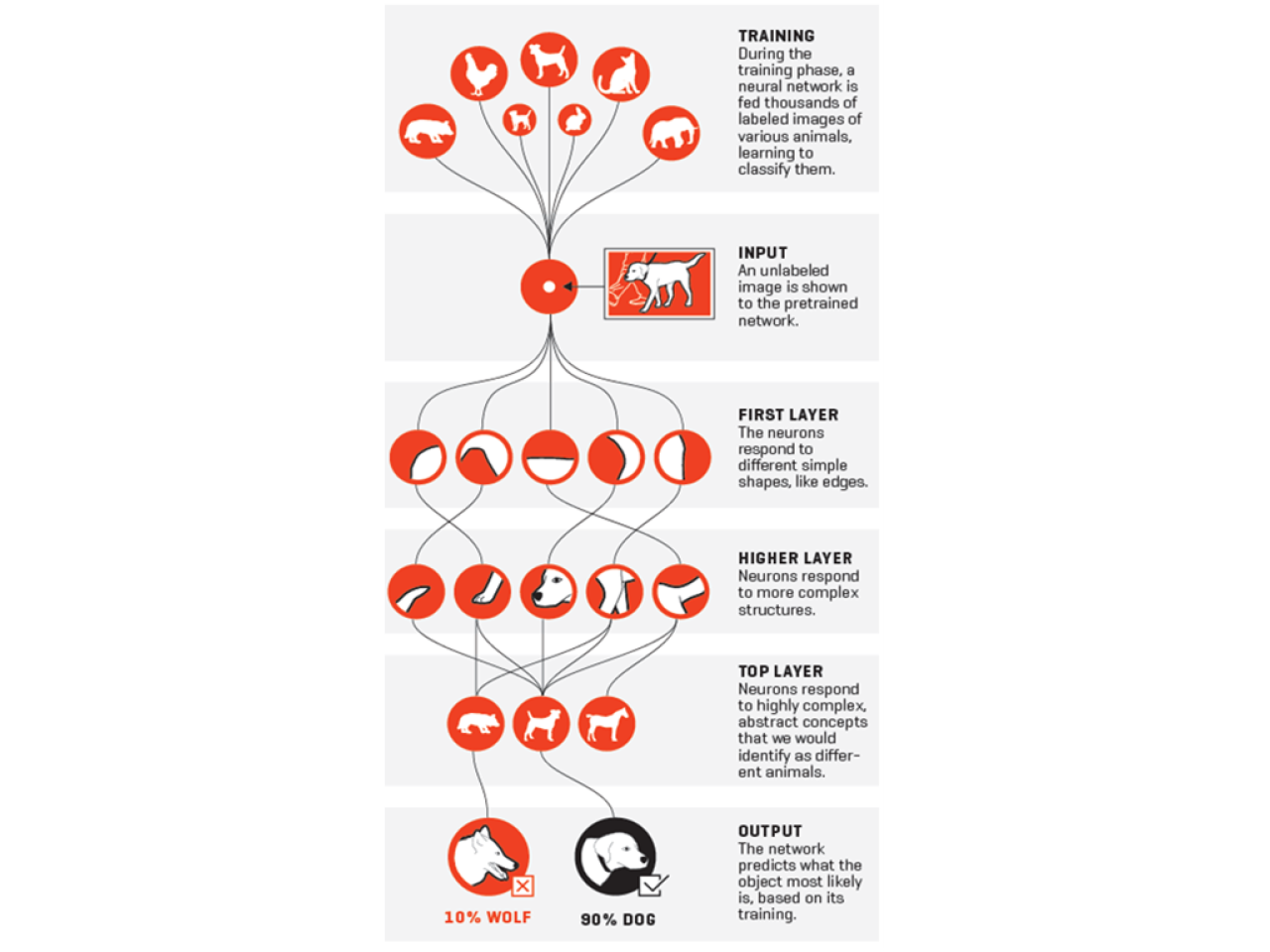

Sono emerse un significativo numero di potenziali applicazioni: - Sviluppo di sistemi Linux-based (acquisizione/fusione di informazioni multi-sensoriali) - Sistemi di power management - Familiarità nel porting ed adattamento dei sistemi operativi - Sviluppo e training di reti neurali (CNN): creazione di data pipeline per la gestione, annotazione ed aumento dei database di immagini - Acceleratori HW basati su FPGA per reti CNN sviluppate con Cafe e TensorFlow È proprio sull'accelerazione di reti neurali che ci si aspetta di avere il maggior numero di potenziali applicazioni.

L'uso di piattaforme embedded di ultima generazione per l'accelerazione delle reti neurali

L'uso di piattaforme embedded di ultima generazione per l'accelerazione delle reti neurali

Le nuove piattaforme multi-core per il settore dell'automazione industriale

Si sono analizzate le caratteristiche di diverse piattaforme HW multi- e many-core, queste ultime basate essenzialmente sulla combinazione di una Main Processing Unit multicore MIMD con un acceleratore many-core SIMD basato su GPU o FPGA. Oltre all'efficienza prestazionale sono stati considerati parametri come efficienza energetica e costo. Il caso di studio per le architetture many-core è stata l'inferenza di reti neurali convoluzionali (CNN) nei sistemi embedded: si sono analizzati sia i requisiti di alcune applicazioni tipiche (e.g. OCR), sia la disponibilità di piattaforme computazionali e di ambienti di sviluppo adeguati. E' emerso il requisito che gli acceleratori di CNN su FPGA siano disponibili anche su piattaforme di fascia più bassa come lo Zynq 7020. Un altro dei requisiti emersi è quello di poter creare un'asimmetria SW a partire da un'architettura HW multi-core omogenea, anche con l'istanziazione multipla di uno stesso kernel (in particolare, RTOS) su core diversi, allo scopo di ottimizzare il partizionamento del carico funzionale. Questa attività ha portato alla realizzazione di diversi dimostratori, basati sia su hypervisor di tipo-1 sia sull'installazione diretta di diversi kernel su diversi subset dei processing core di un SoC.

SACMI S.Coop. Datalogic S.r.l. IMA S.p.A. CIRI ICT INFN TTLab SOFTECH-ICT CRIT

Collaborazioni all'interno del progetto OPEN-NEXT con ricadute su nuovi progetti a commessa.

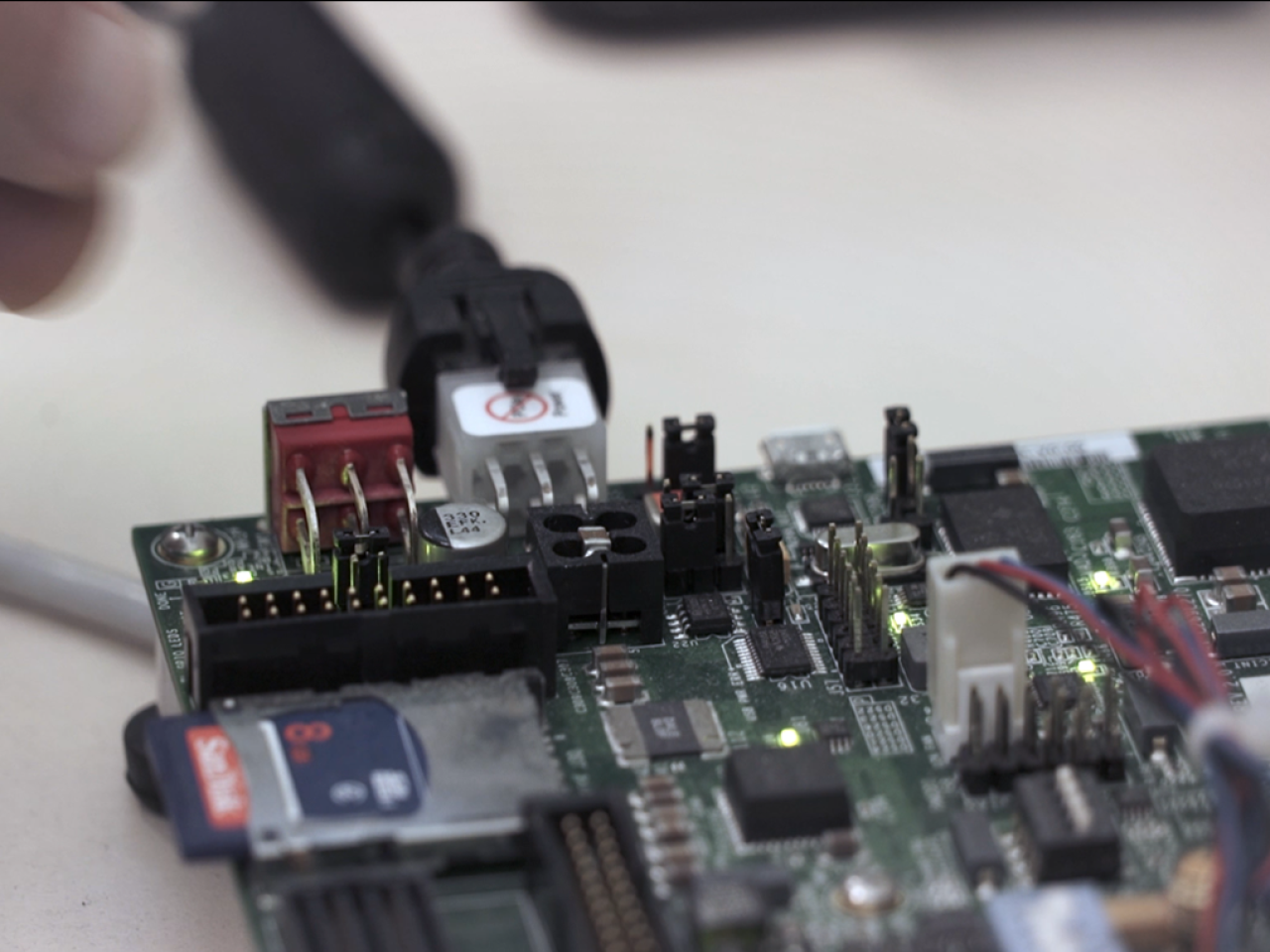

Acceleratore di rete neurale basato su FPGA

Acceleratore di rete neurale basato su FPGA